来源:全球半导体观察整理 原作者:奉颖娴

在3月22日召开的GTC大会上,英伟达宣布与台积电、ASML、新思科技(Synopsys)合作,将加速运算技术用于芯片制造环节的计算光刻中,并推出用于计算光刻的软件库cuLitho。

众所周知,英伟达是知名GPU与人工智能芯片厂商,在本次GTC大会上,英伟达也推出了包括H800等在内的重磅产品。不过,与发布GPU芯片这类常规操作相比,显然英伟达宣布跨界进军芯片制造更易引发业界关注。

英伟达cuLitho旨在将计算光刻提速并降低功耗,助力2纳米以及更先进制程芯片的生产。英伟达透露,cuLitho能够将计算光刻的速度提高到原来的40倍。例如英伟达H100 GPU的制造需要89块掩膜板,在CPU上运行时,处理单个掩膜板需要两周时间,而在GPU上运行cuLitho只需8小时。同时,通过GPU加速计算光刻过程,也可进一步降低能耗。

目前,台积电、ASML与Synopsys均已参与进该项技术中。

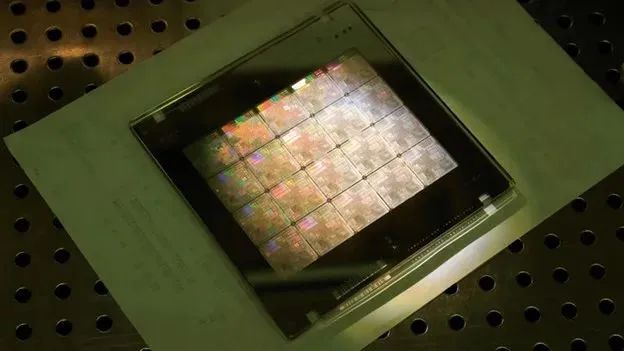

△Source:英伟达官网

英伟达表示,通过将cuLitho软件库集成至台积电的制造流程中,并结合Synopsys的EDA软件,ASML也计划将GPU支持整合到所有的计算光刻软件产品中。在几大芯片供应链巨头共同合作下,可推动半导体行业向更先进芯片制程进军,加速芯片上市时间,提高晶圆厂运行效率,以推动制造过程的大型数据中心的能源效率来改善芯片生产。

上述新闻中,计算光刻被反复提及。这项技术是什么?为何对先进制程芯片生产如此重要?在回答这两个问题前,我们需要先谈摩尔定律。

摩尔定律最常被表述为半导体芯片可容纳的晶体管数量呈倍数增长,而实现晶体管数量翻倍有三个重要手段:增加芯片面积、缩小元件尺寸以及优化器件电路设计。

△Source:英伟达官网

其中,元件尺寸缩小在很大程度上是由光刻工艺和技术的发展推动的。光刻阶段,晶圆会被放入光刻机中,被暴露在深紫外光(DUV)下,光线会通过“掩模版”投射到晶圆上,光刻机的光学系统将掩模版上设计好的电路图案缩小并聚焦到晶圆上的光刻胶,当光线照射到光刻胶上时,会产生化学变化,将掩模版上的图案印制到光刻胶涂层上。

这不是一项简单的工作,粒子干扰、折射和其他物理或化学缺陷都有可能在这一过程中发生,半导体厂商需要修正掩模版上的图案来优化最终的曝光图案。而当芯片越来越小,分辨率缩小到纳米量级时,投影到晶圆上的图形结构会变形,因而需要用到计算光刻这种重构掩模图形的技术。

资料显示,计算光刻主要通过软件对整个光刻过程进行建模和仿真,以优化光源形状和掩膜板形状,缩小光刻成像与芯片设计差距,从而使光刻效果达到预期状态。

光刻机龙头ASML在其公众号上介绍,“计算光刻将算法模型与光刻机、测试晶圆的数据相结合,从而生成一个和最终曝光图案完全不同的掩模版设计,但这正是我们想要达到的,因为只有这样才能得到所需要的曝光图案。”

正是在计算光刻等先进技术助力下,摩尔定律得以不断延续,芯片也不断变小,先进制程芯片得以不断生产。目前晶圆代工厂商已经开始量产3纳米芯片,而在计算光刻助力下,2纳米芯片生产也将成为可能。

英伟达透露,借助cuLitho,台积电可以缩短原型周期时间,提高晶圆产量,减少芯片制造过程中的能耗,并为2纳米芯片生产做好准备。据悉台积电将于今年6月开始对cuLitho进行生产资格认证,并会在2024年对2纳米制程开始风险性试产,2025年开始量产。

2纳米不是芯片生产的终点,2022年5月,IMEC(微电子研究中心)对外公布了1纳米以下至2埃米(A2)的半导体工艺技术和芯片设计的路径。按照规划,到2036年业界有望初步投产0.2nm工艺芯片。

芯片尺寸不断缩小,计算光刻未来发展空间广阔。除此之外,延续摩尔定律,实现更小芯片生产也需要更多先进技术,比如晶体管技术方面,IMEC认为,现有的FinFET只能维持到N3(3纳米)工艺,之后的N2(2纳米)、A14(1.4纳米)将转向GAA环绕栅极、Nanosheet纳米片技术,而再往后的A10(1纳米)、A7(0.7纳米)会改用Forksheet。

封面图片来源:拍信网