来源:TechNews科技新报

近日,比利时微电子研究中心(IMEC)发表1纳米以下制程蓝图,分享对应晶体管架构研究和开发计划。

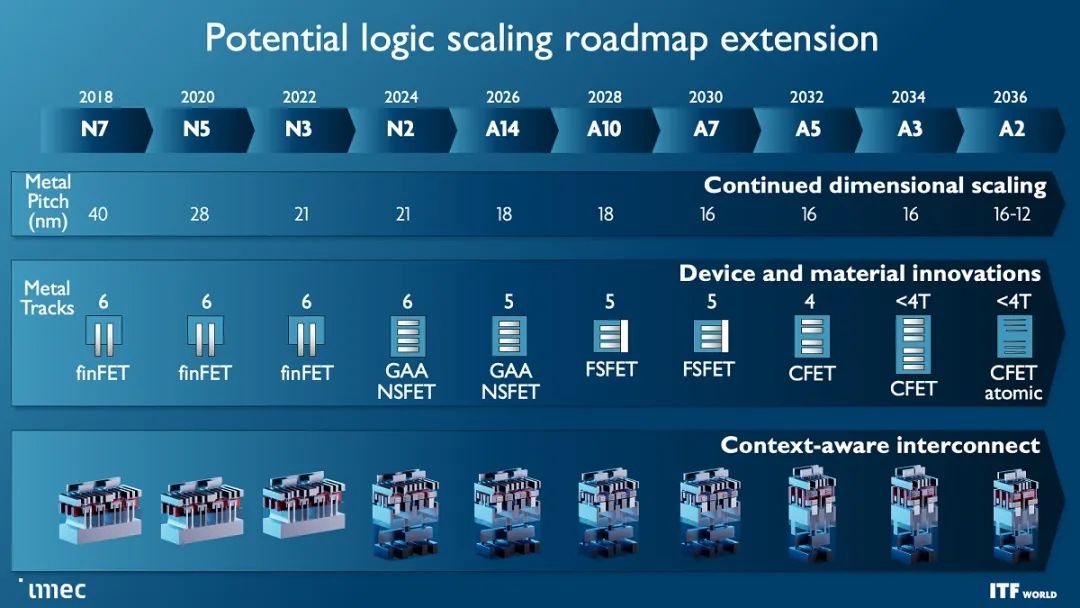

外媒报导,IMEC制程蓝图显示,FinFET晶体管将于3纳米到达尽头,然后过渡到Gate All Around(GAA)技术,预计2024年进入量产,之后还有FSFET和CFET等技术。

△Source:IMEC

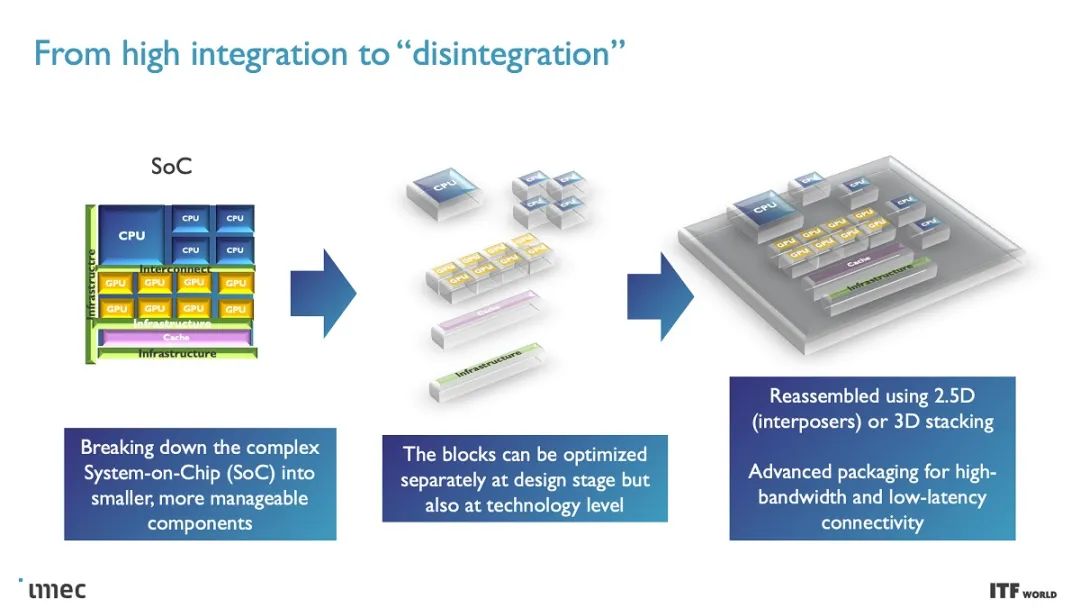

随着时间发展,转移到更小的制程节点会越来越贵,原有的单芯片设计方案让位给小芯片(Chiplet)设计。IMEC的制程发展愿景,包括芯片分解至更小,将缓存和存储器分成不同的晶体管单元,然后以3D排列堆叠至其他芯片功能上。这方法严重依赖后端供电网络(BPDN),将所有供电改到晶体管背面。

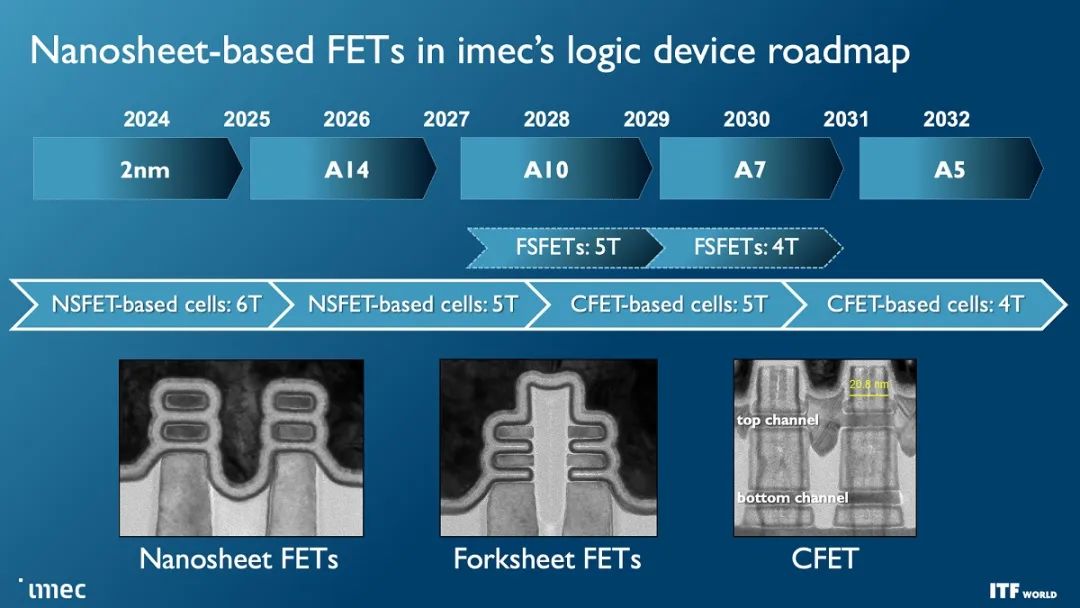

△Source:IMEC

借助系统技术合作最佳化,IMEC重新思考设计过程,对系统和目标应用需求建立结构模式,然后利用这些知识提供资讯设计芯片。芯片拆分为独立单元,以使用不同类型晶体管最佳化每个单元的性能特征,从而降低成本。其目标之一就是将缓存及存储器拆分到独立3D堆叠设计层,降低芯片堆叠的复杂性。

△Source:IMEC

“CMOS 2.0”制程被认为是通往真正3D芯片之路,目前AMD利用3D V-Cache技术将L3暂存堆叠在计算芯片顶部以增加容量。而IMEC的想法则是将整个缓存层次包含于自己架构,L1、L2和L3缓存垂直堆叠在构成处理核心的晶体管上。每层缓存都将用最适合的晶体管创建,由于SRAM微缩大幅减缓,这意味着可以让SRAM未来使用旧节点以降低成本,理想情况下3D堆叠还可帮助缓解与大型缓存相关的延迟问题。

封面图片来源:拍信网